# $\Longrightarrow$ Silvertel

# **Ag6810**

Power Sourcing Equipment

PoE Module

#### **Features**

- Type 4 PSE (PoE++) with up to 95W output

- Configurable as single port Type 2, 3 or 4 output or dual Type 1 or 2 ports

- ➤ IEEE802.3bt Compliant, for use with IEEE802.3bt/at/af PoE devices.

- Single power rail feed

- Small SMT package size 28mm x 18mm x 5mm

- Low cost

- Minimal (low cost) external components required

- > Over-current and short circuit protection

- Output disable

- Industrial temperature range

- > Silvertel "design-in" assistance

# **Description**

The Ag6810 is a single channel or dual channel Power Sourcing Equipment (PSE) module designed for use in Power over Ethernet (PoE) applications with a wide range of power levels from 15.4W (IEEE802.3af), 30W (IEEE802.3at) up to 95W (IEEE802.3bt) power levels.

The Ag6810 is aimed at a wide range of applications requiring PSE functionality such as, IP Cameras, AV distribution, IoT, home networking and industrial Ethernet.

Ag6810 is a self-contained module, requiring only a single supply voltage and just a few external components to provide a simple and cost-effective Power Sourcing Equipment (PSE) application.

# **Table of Contents**

| 1  | Proc       | luct Overview                                | . 3 |

|----|------------|----------------------------------------------|-----|

|    | 1.1        | Ag6810 Product Selector                      |     |

|    | 1.2        | Pin Description                              | . 4 |

| 2  | Fun        | ctional Description                          | . 5 |

|    | 2.1        | Detection Protocol                           |     |

|    | 2.1.1      |                                              |     |

|    | 2.1.2      |                                              |     |

|    | 2.1.3      |                                              |     |

|    | 2.2        | Classification Power Levels                  |     |

|    | 2.2.1      |                                              |     |

|    | 2.3.1      | Power Supply                                 |     |

|    | 2.3.1      | Option Configuration                         |     |

|    | 2.4.1      |                                              |     |

|    | 2.5        | Port Connections                             |     |

|    | 2.6        | Power Dissipation                            |     |

|    | 2.6.1      |                                              |     |

|    | 2.6.2      |                                              |     |

|    | 2.7        | Output Power                                 |     |

|    | 2.7.1      |                                              |     |

|    | 2.7.2      | · · · · · · · · · · · · · · · · · · ·        | 13  |

|    | 2.8        | Status Output                                | 14  |

|    | 2.8.1      |                                              |     |

| _  | 2.8.2      |                                              |     |

| 3  |            | mal Considerations                           |     |

| 4  |            | ection1                                      |     |

|    | 4.1<br>4.2 | Input Protection                             |     |

| 5  |            | lerability                                   |     |

| J  | 5.1        | Solder Profile                               |     |

| 6  |            | trical Characteristics                       |     |

| O  | 6.1        | Absolute Maximum Ratings                     |     |

|    | 6.2        | Recommended Operating Conditions             |     |

|    | 6.3        | Electrical Characteristics                   | 10  |

| 7  |            | Kage                                         |     |

| 8  |            | ering Code                                   |     |

| U  | Olu        | 7 mg 00uc                                    |     |

| Fi |            | le of Figures                                | 3   |

|    |            | ypical Connection Diagram                    |     |

|    |            | Ag6810 Package Format                        |     |

|    |            | Single Signature Detection Profile           |     |

|    |            | Dual Signature Detection Profile             |     |

|    |            |                                              |     |

|    |            | EEE802.3bt Classification Timing             |     |

|    | _          | OPTION pin connections                       |     |

|    |            | Output Disable                               |     |

|    |            | Power Dissipation vs Output Current          |     |

|    |            | Idle Power Draw                              |     |

|    |            | STATUS Output Configuration                  |     |

|    |            | STATUS Output at Port Connect and Disconnect |     |

|    | _          | STATUS Output on Fault Condition             |     |

|    |            | Package Dimensions                           |     |

| Fi | aura 15.   | Land Pattern                                 | 20  |

# 1 Product Overview

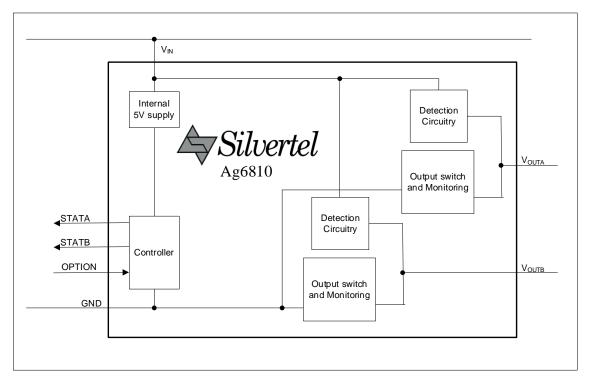

Figure 1: Block Diagram

**Figure 2:Typical Connection Diagram**

# 1.1 Ag6810 Product Selector

| Part Number <sup>1</sup> | Output Power (W) | Marking <sup>2</sup> |

|--------------------------|------------------|----------------------|

| Ag6810                   | 15.4W - 95W      | abc                  |

#### **Table 1: Ordering Information**

- Note 1: Complies with the European Directive 2011/65/EU for the Restriction of use of certain Hazardous Substances (RoHS) including Directive 2015/863 published in 2015, amending Annex II of Directive 2011/65/EU. Moisture Sensitive Level 1 and HBM 1.

- Note 2: The first letter, a, indicates the week as A-Z with uppercase being weeks 1-26, lower case weeks 27-52. The second letter, b, indicates the year in uppercase A-Z starting from 2020. The final letter, c, is a Silvertel reference.

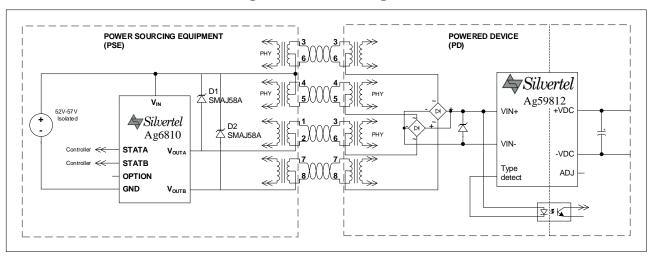

#### 1.2 Pin Description

Figure 3: Ag6810 Package Format

| Pin# | Name              | Description                                                                                                                              |

|------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | V <sub>IN</sub>   | Main Power Supply. This pin connects to an isolated supply and to the centre taps of the high side conductor pairs of the Ethernet cable |

| 2    | OPTION            | <b>Option select pin</b> . A resistor should be fitted to select the power and class profile required. (see section 2.4)                 |

| 3    | STATA             | Status Output. This output shows the status of the output VoutA                                                                          |

| 4    | STATB             | Status Output. This output shows the status of the output V <sub>OUTB</sub>                                                              |

| 5    | GND               | Power Supply Return. Return Path for the isolated power supply.                                                                          |

| 6    | Vouta             | Port Output. This pin monitors the line and enables power delivery to a valid Powered Device (PD)                                        |

| 7    | V <sub>ОUТВ</sub> | Port Output. This pin monitors the line and enables power delivery to a valid Powered Device (PD)                                        |

**Table 2: Pin Descriptions**

# **2 Functional Description**

#### 2.1 **Detection Protocol**

To prevent damage from occurring to non-PoE compatible devices that are connected to a PSE, the IEEE802.3 specification requires that the PSE only provides power after the detection of a PoE enabled device and remove power if the device has been disconnected.

To detect the presence of a PoE enabled device, the PSE should periodically check for a valid PoE signature. If a valid PoE signature is detected. The PSE will then proceed with the multistage classification waveform to determine the power level required from the connected device.

If both outputs of the Ag6810 are not powering a device, the Ag6810 will check the option configuration set by the OPTION pin prior to performing a detection profile, see section 2.4: Option Configuration for details.

If the Ag6810 detects an invalid response in either the signature or classification events the Ag6810 will abort the current identification protocol and flag 'Device Identification Error' on the relevant status output before restarting the detection after a 2 second delay, see section 2.8: Status Output for more details.

#### 2.1.1 Connection check

The first stage of the detection profile is to perform a connection check to determine whether the device connected is a single or dual signature device.

If a single signature device is detected, the Ag6810 will check for a valid signature on both pairsets prior to proceeding with the classification stage.

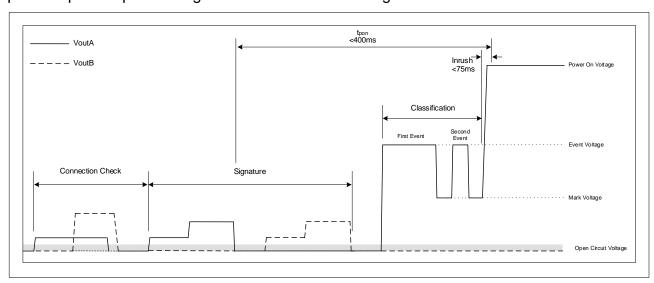

**Figure 4: Single Signature Detection Profile**

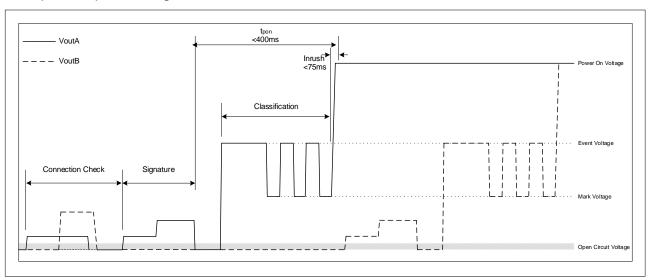

If a Dual Signature device is detected, the full detection profile and power up will occur on  $V_{outA}$  prior to performing the detection check on  $V_{outB}$ .

Figure 5: Dual Signature Detection Profile

#### 2.1.2 Signature Detection

An IEEE802.3 compliant PD should present a nominal  $25k\Omega$  signature resistance. This is detected by applying two voltages between 2.8V and 10V. If the Ag6810 does not see a valid signature on either pairset, it will disconnect, waiting approximately 2 seconds before trying again.

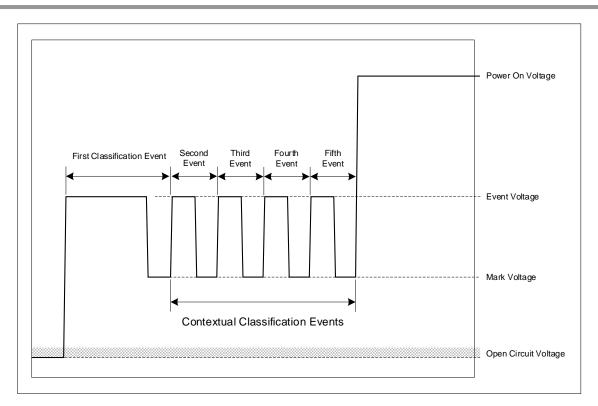

#### 2.1.3 Classification

On detection of a valid signature on a pairset, the Ag6810 will then interrogate the PD to determine the requested Power Class. This is performed using multiple event process, with additional events added with the detection of higher power requests. For example, when connected to a single signature device requesting class of 0,1,2 or 3, the Ag6810 will only output a single classification event prior to applying power, as detailed in Table 3: PSE Single Signature Output Power. The number of Classification events can be used by the PD to determine if it is being supplied with enough power.

The Ag6810 supports the lower MPS requirement added in the IEEE802.3bt amendment, this is indicated to the PD by producing an elongated first classification pulse.

Figure 6:IEEE802.3bt Classification Timing

#### 2.2 Classification Power Levels

The power levels of PoE are separated into several classes and types. The power levels contained in the first implementation of PoE to the IEEE802.3 specification, referred to as Type 1 devices, are for applications ranging up to 12.95W. There are four classification levels for Type 1 devices, Classes 1 to 3 offer incremental power levels. Class 0 is the default for when the PD does not provide a classification power request, the PSE will revert to Class 3 power levels, even if it is capable of providing higher power levels.

Type 2 devices were added in the IEEE802.3at amendment, commonly known as PoE+, this added an additional classification power, doubling the PSEs output power, allowing up to 25.5W applications.

The IEEE802.3bt amendment added two additional device types and four additional classification levels, all of these are commonly referred to as PoE++ devices. These power levels have the additional requirement of power being supplied to all pairs in the cable to reduce transmission losses that could result in overheating of the transmission cable.

If a PD that requests a higher classification power than the PSE can provide, the PSE will provide the connected device with the highest output power it has available. For example, if a device that requests Class 8 is connected to the Ag6810, while the Ag6810 is in Type 2 mode, the Ag6810 will provide the device Class 4 power level of at least 30W. The PD is capable of detecting the PSE type during the detection protocol and can limit its power accordingly.

| PSE<br>Type | Compatible<br>Power<br>Classes | PD<br>Requested<br>Class | Number of<br>Class<br>Events | Minimum PSE<br>output power<br>(W) | Guaranteed<br>power available<br>at the PD<br>(W) |

|-------------|--------------------------------|--------------------------|------------------------------|------------------------------------|---------------------------------------------------|

|             |                                | 0                        | 1                            | 15.4                               | 12.95                                             |

| 1           | 0-3                            | 1                        | 1                            | 4                                  | 3.84                                              |

| '           |                                | 2                        | 1                            | 7                                  | 6.49                                              |

|             |                                | 3                        | 1                            | 15.4                               | 12.95                                             |

| 2           | 0-4                            | 4                        | 2/3                          | 30                                 | 25.5                                              |

| 2           | 0-6                            | 5                        | 4                            | 45                                 | 40                                                |

| 3           |                                | 6                        | 4                            | 60                                 | 51                                                |

| 4           | 0.8                            | 7                        | 5                            | 75                                 | 62                                                |

| 4           | 0-8                            | 8                        | 5                            | 90                                 | 71.3                                              |

**Table 3: PSE Single Signature Output Power**

When a dual signature device is detected, the classification request for each pairset is interrogated independently. If valid dual-signature classification current draw is detected, the Ag6810 will perform either three or four classification pulses, to correctly identify to the PD that it is powered by a dual signature PSE capable of supplying the requested power levels.

| PD Pairset<br>Requested<br>Class | Number of<br>Class<br>Events | Minimum PSE output<br>power on Pairset<br>(W) | Guaranteed power<br>available on Pairset at<br>the PD<br>(W) |  |  |

|----------------------------------|------------------------------|-----------------------------------------------|--------------------------------------------------------------|--|--|

| 0                                | 1                            | 15.4                                          | 12.95                                                        |  |  |

| 1                                | 3                            | 4                                             | 3.84                                                         |  |  |

| 2                                | 3                            | 7                                             | 6.49                                                         |  |  |

| 3                                | 3                            | 15.4                                          | 12.95                                                        |  |  |

| 4                                | 3                            | 30                                            | 25.5                                                         |  |  |

| 5                                | 4                            | 45                                            | 35.6                                                         |  |  |

**Table 4: PSE Dual Signature Output Power**

#### 2.2.1 Data Link Layer Classification and Autoclass

Data Link Layer Classification and Autoclass are optional features of the PoE specification, designed to allow power budgeting in PSEs where the power supply does not have the available power to supply all PoE enabled ports. Both of these features allow power budgeting by allowing the PD to request its power level in more granular increments.

As the Ag6810 is designed for single or dual port applications. It is expected that the power supply will have sufficient power output to cover the maximum power throughput of the module, meaning power budgeting is not necessary. For this reason, these features have not been implemented in the Ag6810.

#### 2.3 **Power Supply**

The Ag6810 requires only a single supply rail. In order to conform to the IEEE802.3 specification isolation requirements, this supply should be isolated from any accessible external conductors including mains ground.

If the power supply has a peak output much greater than 100W, we would recommend fitting a fuse to the positive output rail of the power supply.

#### 2.3.1 Under Voltage Lockout

For operation in Type 1 mode, for applications up to 15.4W, the supply voltage should be between 45V and 57V.

For operation in Type 2 mode for applications up to 30W, the supply voltage should be between 51V and 57V.

For operation in Type 3 and 4 modes the minimum supply voltage is 53V to comply with the permitted transmission voltage of 52V in the IEEE802.3 specification.

The Ag6810 will remove power from the port if the supply voltage drops below the undervoltage lockout threshold. The module's detection procedure will be suspended and flag as undervoltage as per section 2.8 Status Output until the supply voltage returns to a voltage exceeding the undervoltage lockout threshold hysteresis.

#### 2.4 **Option Configuration**

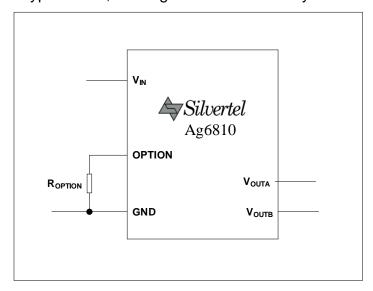

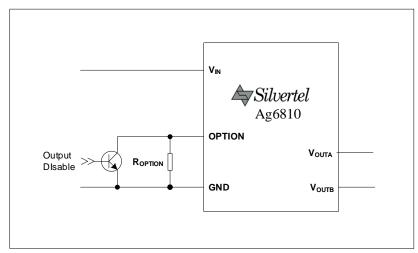

The Ag6810 can be set to operate one of several different modes configuring hardware power limits for use in a variety of applications, this is configured by connecting a resistance between the OPTION pin and GND, as shown in Figure 7.

If there is an open circuit on the OPTION pin, the Ag6810 will default to operation as an IEEE802.3 compliant Type 4 PSE, offering at least 90W to any device requesting class 8.

Figure 7: OPTION pin connections

#### **Power Sourcing Equipment Module**

|                                      | Option Application resistor IEEE802.3 (ROPTION) Compliance |             | C               | Connected                |                       |

|--------------------------------------|------------------------------------------------------------|-------------|-----------------|--------------------------|-----------------------|

| Mode                                 |                                                            |             | Typical power*1 | Highest Class<br>Request | pairsets <sup>2</sup> |

| Port Disable                         | Ω0                                                         | -           |                 | -                        |                       |

| Dual Type 1                          | 16K                                                        | Compliant   | 2 x 20W         | 3                        | Either <sup>3</sup>   |

| Dual Type 2                          | 43ΚΩ                                                       | Compliant   | 2 x 36W         | 4                        | Either <sup>3</sup>   |

| Dual Type 3 <sup>4</sup>             | 75ΚΩ                                                       | Proprietary | 2 x 75W         | 6                        | Both <sup>3</sup>     |

| Single Type 2 (at)                   | 130ΚΩ                                                      | Compliant   | 36W             | 4                        | Either                |

| Single Type 3 (bt)                   | 240ΚΩ                                                      | Compliant   | 75W             | 6                        | Both                  |

| Single High Power (bt+) <sup>5</sup> | 620ΚΩ                                                      | Proprietary | 110W            | 8                        | Both                  |

| Single Type 4 (bt)                   | Open Circuit                                               | Compliant   | 95W             | 8                        | Both                  |

- Note 1: Per port power, dependent on Supply Voltage, See section 2.6: Power Dissipation for details.

- Note 2: See section 0

- Note 3: Port Connections for details.

- Note 4: Connected to separate ports

- Note 5: Compatible with IEEE802.3bt single signature PDs. Can be used in proprietary high-power applications using two ports where the connected powered devices have been specified and tested to be compatible with operation in this mode.

- Note 6: Compatible with standard IEEE802.3bt PDs. Reserved for proprietary applications where the 99.9W limitation needs to be exceeded, this mode applies a 1A limit on each pairset when a Class 7 or 8 single signature PD or a Class 5 Dual Signature PD request has been detected. This limit is within the typical current ratings of IEEE802.3bt rated components.

**Table 5: Option Select**

#### 2.4.1 Output Disable

In some applications it may be desirable to disable the outputs of the module. This can be implemented with a transistor in parallel with the option resistor, if fitted, to pull the OPTION pin to GND, as shown in Figure 8: Output Disable. This will disable both outputs in single port and dual port modes of operation.

**Figure 8: Output Disable**

#### 2.5 **Port Connections**

The eight conductors of the Ethernet link are divided into two pairsets. The two pairs terminating in pins 1,2,3 and 6, usually called the 'Data Pairs', are grouped as a pairset. With the other conductors, usually called the 'Spare Pairs', as the other pairset. In Gigabit Ethernet (GbE or 1000Base-T) both pairsets are used for data transmission

Power rails are applied to the Ethernet link conductors via the centre tap of the data transformer, as shown in Figure 2:Typical Connection Diagram. This results in the power being applied in common across the data signals, preventing interference on the data transmission.

For applications using Type 3 or 4 modes, power should be applied to all eight conductors in the Ethernet link. For applications in the Type 1 or 2 modes, only one of the two pairsets should be connected for power transmission. This allows the second output supply power to a second port if desired.

For compliance with the IEEE802.3 specification, when in Type 4 mode, one of the modules outputs should be connected to the conductor pair containing conductors 3 & 6. The other module output should be connected to the conductor pair containing conductors 4 & 5. With the two pairs containing conductors 1 & 2 and conductors 7 & 8 should be connected to V<sub>in</sub>. In all other modes the polarity of the power between the pairs of each pairset is not specified in the IEEE802.3 specification.

## 2.6 **Power Dissipation**

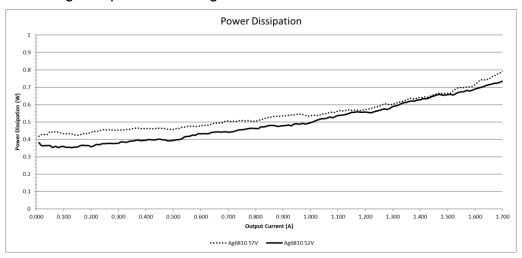

#### 2.6.1 Power Dissipation

The Ag6810 dissipates little power, in a Type 8 application drawing 90W will result in less than 800mW being dissipated in the Ag6810.

**Figure 9: Power Dissipation vs Output Current**

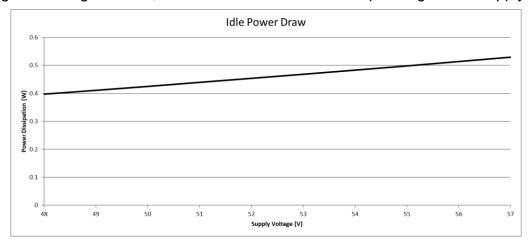

#### 2.6.2 Idle power Dissipation

While the Ag6810 is not powering a device, whether due to no PoE device being detected or the Ag6810 being disabled, it will draw 0.40W - 0.53W depending on the supply voltage.

Figure 10: Idle Power Draw

#### 2.7 Output Power

The maximum available power to a PD is defined by the current on the cable pairs, as a result higher supply voltages will allow for more power to be available to the Powered Device. This is due to the IEEE802.3 specification requiring the transmission current to be the primary power limiting criteria of Power Over Ethernet.

#### 2.7.1 Output Current Limits

There are two over current mechanisms that the Ag6810 uses to determine whether to remove power to the device, Overload Current and Current Limiting.

#### 2.7.1.1 Overload Current

The overload current allows the maximum cable current to be exceeded for brief periods of time, preventing temporary surges in power draw from triggering power removal due to overcurrent, such as an inrush due to the application waking from a low power mode or a peripheral device being connected.

Exceeding the Overload Current Threshold, IoVLD, for more than Overload Time Limit ToVLD will result in power being removed from the line with the module flagging the Overload Current status. This is in accordance with upper and lower bound current templates detailed in the IEEE802.3 specification.

#### 2.7.1.2 Current Limiting

In the event of a short circuit, or other fault event, the Ag6810 has a current limit where the output current will be capped at the Short Circuit Current Limit, I<sub>LIM</sub>, for the Short Circuit Time Limit, T<sub>LIM</sub>. If the current is still being limited at the end of this time period power will be removed from the line with the module flagging the Short Circuit status.

#### 2.7.2 Maintain Power Signature (MPS)

While the Ag6810 is supplying power to a connected device, it will continuously monitor the output current, not only to prevent over current, but to ensure that the device is still connected; this is referred to as the Maintain Power Signature (MPS).

The standard MPS requirement is that the PSE cannot remove power from the device if there is a continuous current draw greater than 10mA for a period of at least 75ms, after which there can be a period of no current draw for up to 250ms.

The low power MPS that the Ag6810 supports requires 10mA to be drawn for only 6ms, after which there can be a period of 319ms with no current draw for the device to be determined as present.

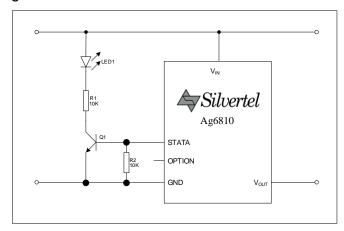

#### 2.8 Status Output

The Ag6810 has two status output that can either be used to illuminate LEDs or passed into a controller. The output of these pins are sourced through a  $47k\Omega$  current limiting resistors to prevent excessive power dissipation in the module. For illuminating an LED, the Status output should be used to drive the gate of a transistor as shown in Figure 11: STATUS Output Configuration

Figure 11: STATUS Output Configuration

STATA will indicate the status of the port or pairset connected to  $V_{\text{OUTA}}$ , STATB will indicate the status of the port or pairset connected to  $V_{\text{OUTB}}$ . The exception to this is when the module is in a single port mode and a single signature PD is connected, in this configuration STATA will indicate the status for both  $V_{\text{OUTA}}$  and  $V_{\text{OUTB}}$  Outputs.

The status output will default to logic 0. If an open circuit is detected on the output, the status output will remain at logic 0 with no pulses. If a non-PoE enabled device is connected to the port, depending on the configuration of the connected device, the status output may or may not provide a single flash every 2 seconds after each detection cycle.

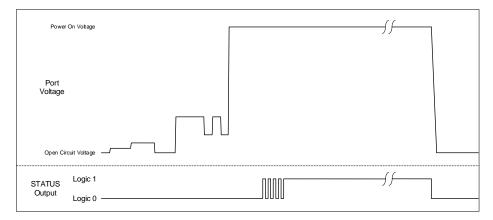

#### 2.8.1 Device Connection and Removal

After the successful detection and power up of a PoE Device, the status output will rise to logic 1, then begin a sequence of 2ms logic 0 pulses to indicate the requested power classification of the powered device, then remain at logic 1 while the device remains powered.

Figure 12: STATUS Output at Port Connect and Disconnect

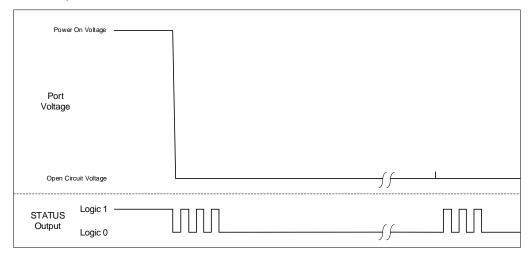

#### 2.8.2 Fault Condition

In the event of a fault the Ag6810 will output a sequence of Logic 1 pulses after power removal as per Table 6: Status Output, it will then repeat the sequence at the end of every detection cycle until the fault condition is no longer present. An example of the STATUS output during a persistent short circuit event occurring on the pairset can be seen in Figure 13: STATUS Output on Fault Condition

Figure 13: STATUS Output on Fault Condition

In addition to the STATUS output reporting when the output ports are connected or disconnected, the STATUS output also reports when a fault has been detected.

| Fault Condition             | Status Pulses (200ms)   |

|-----------------------------|-------------------------|

| Device Identification Error | 1 x Logic 1 Pulse       |

| Input Voltage < UVLO limit  | 2 x Logic 1 Pulses      |

| Short Circuit               | 3 x Logic 1 Pulses      |

| Overload Current            | 4 or 5 x Logic 1 Pulses |

**Table 6: Status Output**

#### 3 Thermal Considerations

The Ag6810 dissipates little power in normal operation, there are no specific requirements for thermal management.

#### 4 Protection

#### 4.1 Input Protection

The Ag6810 has a built-in tranzorb diode across its input to protect the module from most transients from the power supply. If the application requires long cabling between the PSU output and the module or is expected to be used in environments with increased transient intensity, we recommend additional protection is fitted to the input of the module.

It is recommended that a 2A slow blow fuse to be fitted in line with the positive input rail.

#### 4.2 **Output Protection**

To protect the module from voltage transients coming from the RJ45 cable we would recommend fitting a SMAJ58 or higher on each of the Ag6810 outputs as shown in Figure 2:Typical Connection Diagram.

# 5 Solderability

The Ag6810 has been designed with a fully automated assembly process in mind and is lead-free (Pb-free) and RoHS compliant and fully compatible with a Pb-free automated assembly process. The Ag6810 can still be mounted manually using soldering iron or hot air.

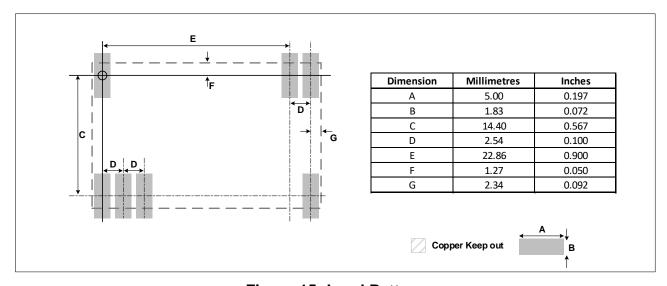

There are no specific requirements regarding stencil thickness or solder paste classification type. Solder mask defined (SMD) pads are preferred over non-solder mask defined (NSMD) pads, the land pattern dimensions are given in Figure 15: Land Pattern.

Minimal thermal relief should be applied to the pads to allow for maximum thermal conductivity without hindering the reflow process, your Process Engineer should be able to provide suitable recommendations.

The Ag6810 requires no components of greater than Moisture Sensitivity level 1, as a result no special processes are required in the reflowing process of the Ag6810.

Note: Do not pass the Ag6810 through the reflow process mounted to the underside of the assembly due to the risk of components falling off the module.

#### 5.1 **Solder Profile**

Below is a typical profile showing how the Ag6810 should be mounted, based on the J-STD-020 standard for Pb-Free applications. Exceeding these specifications may cause damage to the module. All production environments are different therefore please review these guidelines with your process engineer prior to use.

|               | Zone 1 | Zone 2 | Zone 3 | Zone 4 | Zone 5                 | Units     |

|---------------|--------|--------|--------|--------|------------------------|-----------|

| Zone Duration | 42     | 42     | 42     | 42     | 42                     | Seconds   |

| Top Heater    | 150    | 180    | 210    | 240    | 270                    | °C        |

| Bottom Heater | 150    | 180    | 210    | 240    | 270                    | ů         |

| Typical Slope | 2.1    | 1.2    | 1.1    | 0.9    | 0.8                    | °C/Second |

| Airflow rate  | 40     |        |        |        | M <sup>3</sup> /Minute |           |

**Table 7: Solder Profile**

|                            | Min | Max | Units     |

|----------------------------|-----|-----|-----------|

| Soak Time (s)<br>150-180°C | 30  | 90  | Seconds   |

| Time above (s)<br>≥220°C   | 30  | 90  | Seconds   |

| Peak Temperature (°C)      | 230 | 255 | °C        |

| ΔTemperature (°C/s)        | -3  | 3   | °C/Second |

**Table 8: Solder Parameters**

# **6 Electrical Characteristics**

# 6.1 **Absolute Maximum Ratings**

|   | Parameter                  | Symbol          | Min  | Max  | Units |

|---|----------------------------|-----------------|------|------|-------|

| 1 | DC Supply Voltage          | V <sub>DD</sub> | -0.3 | 60   | V     |

| 2 | Storage Temperature        | Ts              | -40  | +100 | °C    |

| 3 | Moisture Sensitivity Level | MSL             | -    | 1    | -     |

Note: Exceeding the above ratings may cause permanent damage to the product. Functional operation under these conditions is not implied. Maximum ratings assume free airflow.

### 6.2 Recommended Operating Conditions

|   | Parameter             | Symbol                             | Min | Тур | Max | Units   |

|---|-----------------------|------------------------------------|-----|-----|-----|---------|

|   |                       | VDD (Type 1 mode)                  | 45  |     |     |         |

| 1 | Input Supply Voltage  | VDD (Type 2 modes)                 | 51  |     | 57  | V       |

|   |                       | V <sub>DD</sub> (Type 3 & 4 modes) | 53  |     |     |         |

| 2 | Operating Temperature | Тор                                | -40 | 25  | 85  | Ta / °C |

# 6.3 Electrical Characteristics

|        | Parameter                               | Sym                                    | Powe      | er Level            | Min   | Тур      | Max   | Units |       |       |       |       |       |       |       |         |                                |  |     |  |

|--------|-----------------------------------------|----------------------------------------|-----------|---------------------|-------|----------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------|--------------------------------|--|-----|--|

| 1      | VDD Idle Supply Current                 | I <sub>DD</sub>                        |           |                     |       | 5.5      |       | mA    |       |       |       |       |       |       |       |         |                                |  |     |  |

| 2      | Signature Detection Voltage             | V <sub>SIGL</sub><br>V <sub>SIGH</sub> |           |                     | 2.7   | 4.5<br>9 | 10.1  | V     |       |       |       |       |       |       |       |         |                                |  |     |  |

| 3      | Valid Signature Range                   | Rsigl                                  |           |                     | 18    |          | 29    | kΩ    |       |       |       |       |       |       |       |         |                                |  |     |  |

| 4      | Classification Event Voltage            | VCLASS                                 |           |                     |       | 17       |       | V     |       |       |       |       |       |       |       |         |                                |  |     |  |

| 5      | Classification Mark Voltage             | VMARK                                  |           |                     |       | 8.3      |       | V     |       |       |       |       |       |       |       |         |                                |  |     |  |

|        |                                         |                                        | CI        | ass 0               | 0     |          | 6.5   |       |       |       |       |       |       |       |       |         |                                |  |     |  |

|        |                                         |                                        | CI        | ass 1               | 6.6   |          | 14.6  |       |       |       |       |       |       |       |       |         |                                |  |     |  |

| 6      | Classification Threshold<br>Current     | ICLASS                                 | CI        | ass 2               | 14.6  |          | 23.2  | mA    |       |       |       |       |       |       |       |         |                                |  |     |  |

|        | Guitone                                 |                                        | CI        | ass 3               | 23.2  |          | 33.5  |       |       |       |       |       |       |       |       |         |                                |  |     |  |

|        |                                         |                                        | CI        | ass 4               | 33.5  |          | 47.9  |       |       |       |       |       |       |       |       |         |                                |  |     |  |

| 7      | Classification Current Limit            | Iclassli<br>m                          |           |                     |       | 57.3     |       | mA    |       |       |       |       |       |       |       |         |                                |  |     |  |

| 8      | Maintain Power Signature                | I <sub>MPS</sub>                       |           |                     | 5     | 6        | 10    | mA    |       |       |       |       |       |       |       |         |                                |  |     |  |

|        |                                         |                                        | Class 0-3 |                     |       | 410      |       |       |       |       |       |       |       |       |       |         |                                |  |     |  |

|        |                                         | lovld                                  | Class 4   |                     |       | 700      |       |       |       |       |       |       |       |       |       |         |                                |  |     |  |

|        |                                         |                                        | Olara 5   | Single<br>Signature |       | 1410     |       |       |       |       |       |       |       |       |       |         |                                |  |     |  |

| 9      | Overload Current Threshold              |                                        | lovld     | IOVLD               | lovld | lovld    | lovld | lovld | lovld | lovld | lovld | lovld | lovld | lovld | IOVLD | Class 5 | Dual<br>Signature <sup>1</sup> |  | 920 |  |

|        |                                         |                                        | Class 6   |                     |       | 1410     |       |       |       |       |       |       |       |       |       |         |                                |  |     |  |

|        |                                         |                                        | Cla       | ass 7¹              |       | 1860     |       |       |       |       |       |       |       |       |       |         |                                |  |     |  |

|        |                                         |                                        | Cla       | ass 8¹              |       | 1860     |       |       |       |       |       |       |       |       |       |         |                                |  |     |  |

| 10     | Overload Time Limit                     | Tovld                                  |           |                     |       | 60       |       | ms    |       |       |       |       |       |       |       |         |                                |  |     |  |

| 11     | Short Circuit Current Limit<br>Per Pair | Ішм                                    |           |                     |       | 1.4      |       | А     |       |       |       |       |       |       |       |         |                                |  |     |  |

| 12     | Short Circuit Time Limit                | TLIM                                   |           |                     |       | 3        |       | ms    |       |       |       |       |       |       |       |         |                                |  |     |  |

|        |                                         |                                        | Туре      | 1 Mode              |       | 42       |       |       |       |       |       |       |       |       |       |         |                                |  |     |  |

| 13     | Under Voltage Lockout<br>Threshold      | Vuvlo                                  | Туре      | 2 Modes             |       | 48       |       | V     |       |       |       |       |       |       |       |         |                                |  |     |  |

|        | mesnoia                                 |                                        | Type 3    | & 4 Modes           |       | 50.5     |       |       |       |       |       |       |       |       |       |         |                                |  |     |  |

| 14     | STATA and STATB Output                  | V <sub>OH</sub><br>V <sub>OL</sub>     |           |                     |       | 0.3      | 5     | V     |       |       |       |       |       |       |       |         |                                |  |     |  |

| Note 1 | : Dependent on supply voltage, Figure   | given for 52\                          | / supply  |                     | ·     |          |       |       |       |       |       |       |       |       |       |         |                                |  |     |  |

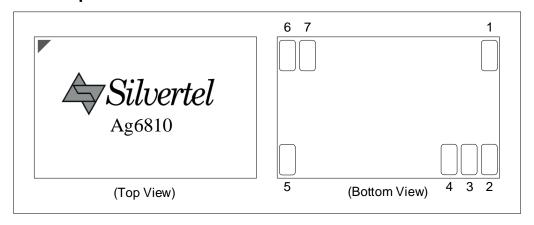

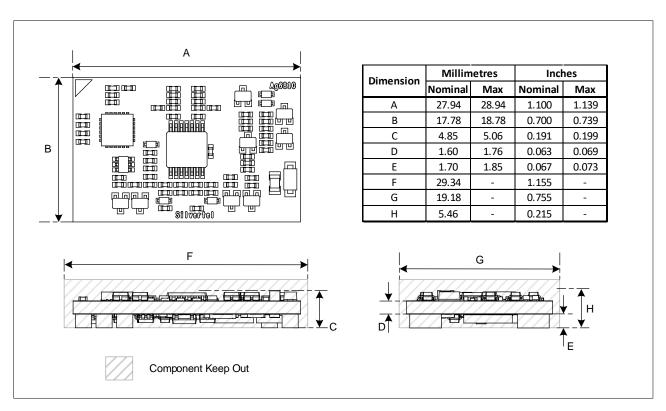

# 7 Package

**Figure 14: Package Dimensions**

Figure 15: Land Pattern

# 8 Ordering Code

|           | Ag6810-157 | ΓR |

|-----------|------------|----|

| Series    |            |    |

| Packaging |            |    |

blank = Tray, 15TR = 15" Reel

Information published in this datasheet is believed to be correct and accurate. Silver Telecom assumes no liability for errors which may occur or for liability otherwise arising out of use of this information or infringement of patents which may occur as a result of such use. No license is granted by this document under patents owned by Silver Telecom or licensed from third parties by Silver Telecom. The products, their specification and information appearing in this document are subject to change by Silver Telecom without notice.